研究方向:

-

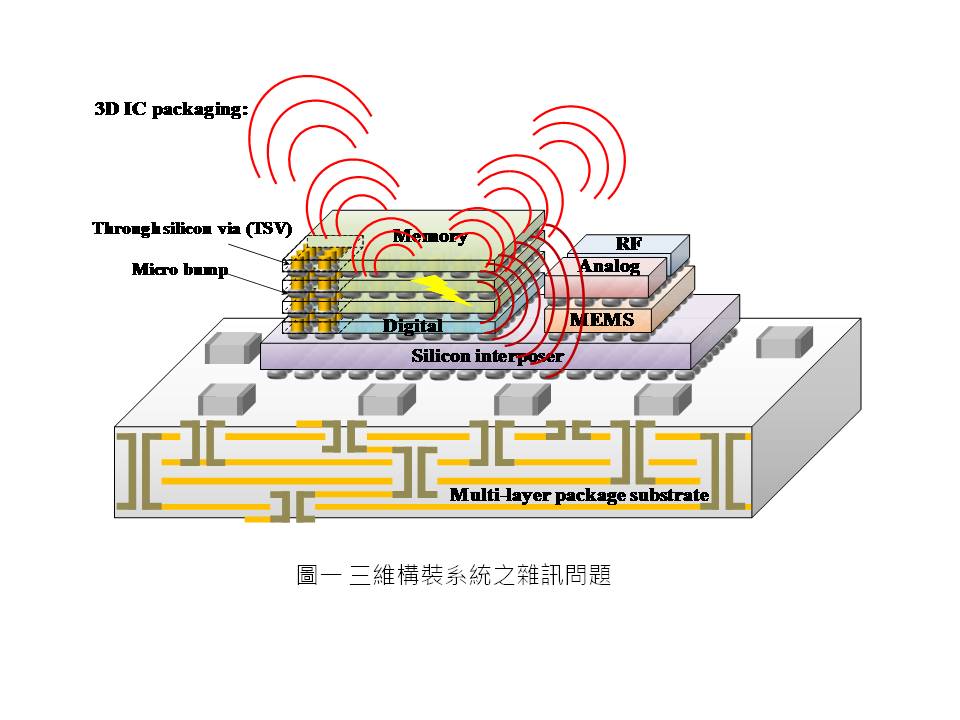

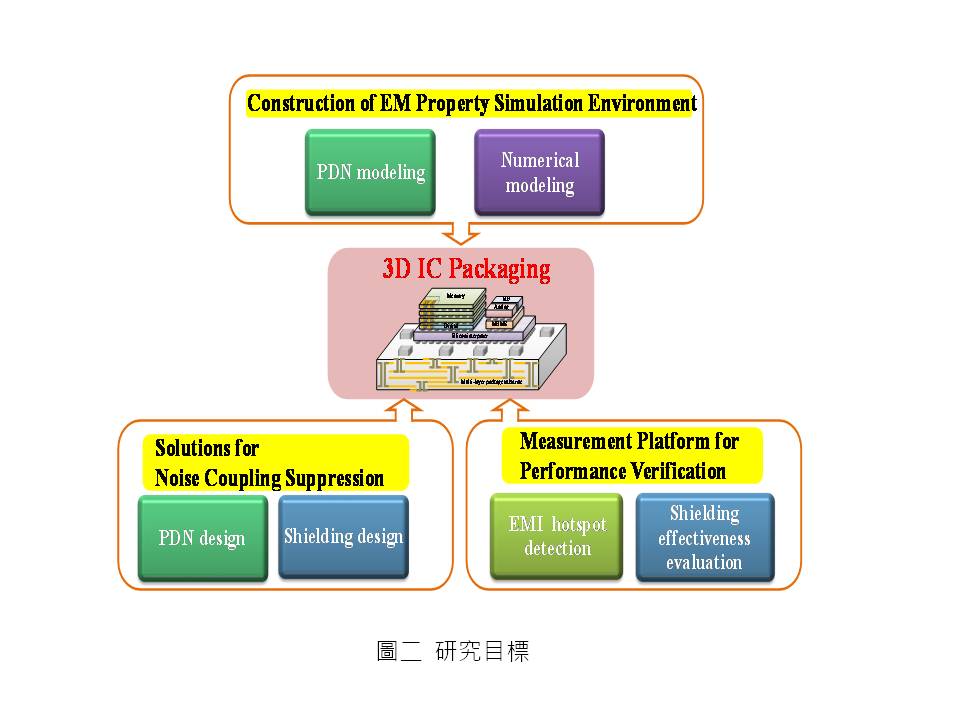

信號及電源完整性分析及設計:3D-IC中穿矽貫孔(TSV)為能達成電路三維化的要角,但它對信號及電源的傳輸也同時造成許多影響。準確的建立3D-IC中PDN的等效電路模型、分析電源雜訊的耦合機制、雜訊 耦合對各個積體電路的影響、以及如何設計PDN以有效降低雜訊耦合,如何設計補償電路以提升信號品質 等均為重要研究方向。

-

電磁遮蔽量測技術:高密度3D-IC易造成顯著之電磁雜訊干擾,亟需使用屏蔽技術加以抑制。傳統量測方 法難以準確評估實際屏蔽效能,因此將研究利用先進天線技術包含寬頻帶晶片探針/天線設計、微小化壓 控自振式主動天線及天線去耦合網路之晶片設計,進行量測技術之改良研究,提升混附輻射之量測準確 度,冀以提供屏蔽技術之良好驗測方法。

-

電磁模擬及分析方法:3D-IC中經常同時具備微小及大型結構,數量級可從微米等級至數毫米等級,如何 正確且有效率的計算及預測3D-IC的電磁雜訊行為一關鍵技術。因此數值模擬演算法需針對取樣格點進行 改良,以取得計算量與準確度的平衡。也將視實際計算結果整理出可以化簡的參數,可減少計算量以改善 效率,建立起一套高效率的3D-IC模擬機制及程式。

-

晶片級近場量技術:測高解析度及高靈敏度近場探針能在3D-IC電路表面量測磁場以作為量測電磁輻射的 重要工具。磁場探針的設計需要有良好的探針屏蔽效應,以免耦合到同一個構裝中其他電路的輻射訊號, 此外,提出探針陣列的設計以期達成縮短量測時間亦為重要研究方向。

|